# VLSI Architecture of Montgomery Modular Multiplier: A Review

<sup>1</sup>Satish kumar, <sup>2</sup>Dr. Bharti Chourasia

<sup>1</sup>M.Tech Scholar, <sup>2</sup>Associate Professor & HOD, <sup>1&2</sup>Department of Electronics & Communication, <sup>1&2</sup>RKDF Institute of Science & Technology, SRK University, Bhopal, India.

*Abstract*: Multiplication is a key operation to perform the processing speed of digital processor. Montgomery multiplication is a strategy for performing quick modular multiplication. This paper presents an outline on execution of Montgomery measured duplication estimation utilizing VLSI design. The Montgomery figuring is a fast particular increase procedure as regularly as conceivable used in cryptographic applications, in which the capability of cryptosystem depends upon the speed of secluded duplication. This audit gives the assessment between different adjustments done in Montgomery particular augmentation.

IndexTerms - Multiplier, Montgomery, Modular, VLSI, Cryptosystem.

# I. INTRODUCTION

Montgomery particular duplication, significantly more regularly inferred as Montgomery increase, is a strategy for performing energetic measured augmentation. Given two numbers an and b and modulus N, the old style measured duplication calculation enlists the twofold width thing stomach muscle mod N, and a brief timeframe later plays out a division, taking away consequences of N to balance the grievous high pieces until the remainder of after a short time not as much as N. Montgomery decrease rather adds consequences of N to balance the low pieces until the outcome is an alternate of a strong (for example intensity of two) unsurprising R > N. By then the low pieces are disposed of, conveying an outcome under 2N. One final unanticipated deduct reduces this to not as much as N. This method keeps up a key decent ways from the multifaceted structure of extra segment digit estimation.

The outcome is the ideal thing allotted by R, which is less seriously structured than it may show up. To duplicate an and b, they are first changed over to Montgomery structure or Montgomery delineation a R mod N and b R mod N. At whatever point replicated, these produce abR2 mod N, and the going with Montgomery decrease produces abdominal muscle R mod N, the Montgomery sort of the ideal thing. Changing over to and from Montgomery structure makes this more slow than the conventional or Barrett decay calculations for a singular duplicate. In any case, when playing out different duplications in movement, as in measured exponentiation, widely appealing outcomes can be left in Montgomery structure and the basic and last changes become an immaterial division of the overall figuring. Different immense cryptosystems, for example, RSA and Diffie–Hellman key trade depend upon math endeavors modulo a colossal number, and for these cryptosystems, the figuring by Montgomery increase is snappier than the open choices.

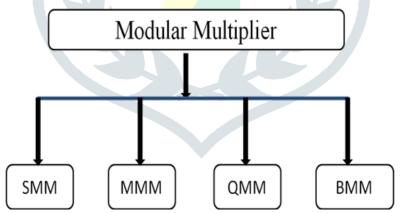

Figure 1: Classification of modular multiplier

In figure 1, showing different types of modular multiplier. Systolic Modular Multiplication (SMM), Montgomery modular multiplier (MMM), Quantum Modular Multipliers (QMM), Barrett Modular Multiplier (MMMM)

**Multiplication:** Cryptographic applications don't use negative numbers; thusly our digit-multiplication circuit performs simply unsigned multiplications. The things are amassed (added to a 32... 50-bit register) yet simply single digits are isolated from these registers and set away in memory.

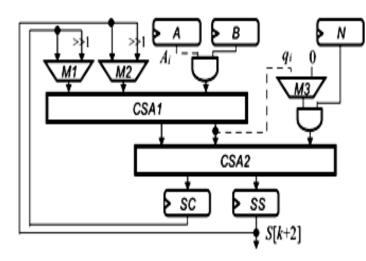

Figure 2: Low cost High performance VLSI architecture

For operand measures in cryptographic applications the school multiplication is the best, requiring essential control. Some speed improvement can be typical from the more caught Karatsuba method, anyway the Toom-Cook 3-way (or past) multiplication is totally for these lengths. A FFT based multiplication takes altogether longer until significantly greater operands (for our circumstance around various occasions slower).

## **II. LITERATURE REVIEW**

**J. Ding et al., [1]** Right now, non-least positive form (NLP) based modular duplication technique that joins Karatsuba and textbook increase is applied in Montgomery modular augmentation, which saves 2 base augmentations contrasted with Karatsuba-just plans and permits pipeline structure to utilize the parallelism in huge modular augmentations.

A. Parihar et al., [2] The proposed multiplier includes and moves just as processes the accompanying two remainders all the while to limit the basic way delay. What's more, the proposed multiplier consolidates two cycles, which require extra middle of the road operands. Right now, execution time and the quantity of clock cycles required for augmentation are limited altogether and additional clock cycles required for format transformation and operand pre-calculation can be neglected.

J. Li et al., [3] proposed engineering keeps up a fast for bigger parallel fields, making it increasingly reasonable to be actualized in huge piece length platforms with a higher security level. Since the multiplier and its fragments work in various piece length and allude to various fields, the proposed engineering can likewise be moved up to a reconfigurable plan to help different field point increase later on.

**W. Dai et al., [4]** show that our work offers a superior proficiency contrasted with the cutting edge works from or more 2048piece operand sizes. For single FFT-based modular increase, it is have accomplished steady running time and got territory inactivity productivity enhancements up to 24.3 percent for 1,024-piece and 35.5 percent for 4,096-piece operands, individually.

**P. Patronik et al., [5]** The outcomes demonstrate that gratitude to littler modular multipliers, RNS math units have littler both region and delay, and, therefore, they permit to accomplish up to over 20% vitality putting something aside for a steady coefficient channel application, up to over 28% for the network augmentation, and up to 27% for Montgomery duplication, contrasted and executions utilizing a positional number-crunching unit.

**S. S. Erdem et al., [6]** In light of this investigation, a proficient digit-sequential Montgomery modular multiplier design utilizing carry save adders is proposed and its unpredictability is exhibited. Right now, carry select adders are utilized to perform two last errands: including carry save vectors speaking to the modular item and subtracting the modulus from this expansion, if further decrease is required.

**P. Chen et al., [7]** The proposed Montgomery calculation utilizes a novel precomputed-modular activity, and the systolic structures dependent on this calculation completely acquire the points of interest brought from the AOP-based center (low register multifaceted nature, low basic way deferral, and low dormancy) with the exception of some minimal equipment overhead brought by a precomputation unit.

**S. NEMA et al., [8]** presents multiplier less CORDIC (Coordinate Rotation Digital Computer) algorithm based on DCT. CORDIC is a main component of shift and add for rotation vector and plan which is usually used for calculation of trigonometric functions. CORDIC algorithm is efficient area and delay compared to existing algorithms. All design are implementation Xilinx 14.1i and verified the result.

**M. Spirits Sandoval et al., [9]** FPGA's standard rationale while keeping a satisfactory performance contrasted and other execution draws near. From the Virtex5 execution, the proposed MM multiplier arrives at a throughput of 242 Mbps utilizing just 219 FPGA cuts and accomplishing a 1024-piece modular increase in  $4.21\mu s$ . This is multiple times less zone assets than comparable related works in the writing with an improved productivity of 7x.

## **III. MONTGOMERY MODULAR MULTIPLICATION ALGORITHMS**

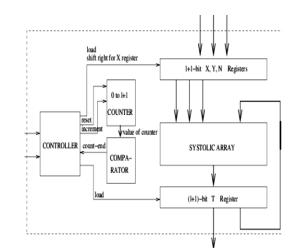

Figure 3: Architecture of the Montgomery modular multiplier circuit

It is expect  $m = \{mn-1 \ mn-2... \ m0\}$  is standardized, that is  $\frac{1}{2} d \le mn-1 < d \text{ or } \frac{1}{2} d n-1 \le m < d n$ . It is ordinarily the situation with RSA moduli. If not, we need to standardize it: supplant m with 2km. A modular decrease step (examined beneath) fixes the outcome: having Rk = a mod 2km determined, Rk - q•m, where q is processed from the leading digits of Rk and 2km. These de/standardization steps are just performed toward the beginning and end of the figurings (if there should be an occurrence of an exponentiation chain), so the amortized expense is irrelevant.

There are a basically 4 estimations used in memory obliged, digit consecutive applications (sharp card, secure co-processors, customer devices, etc.): Interleaved push multiplication and reduction, Montgomery, Barrett and Quisquater multiplications.

#### A. Montgomery multiplication

It is direct and brisk, using perfect to-left divisions. Toward this way there are no issues with passes on (which induce a long way from the took care of digits) or with assessing the rest of wrong, so no correction steps are fundamental. This gives it some 6% speed ideal position over Barrett's decline and over 20% speed advantage over division based abatements. The standard Montgomery multiplication figures the thing in "push demand", yet regardless of all that it can misuse a speedup for squaring. The fundamental hindrance is that the numbers must be changed over to a novel structure before the checks and fixed close to the end, that is, significant pre-and post-handling and extra memory is required.

The thing Stomach muscle can be resolved interleaved with the decline, called the Montgomery multiplication. It needs squaringspeedup as noted already. The guidance  $x = (x+aib+t\cdot m)/d$  is a hover through the digits of B and m from fitting to left, keeping the pass on engendering to the other side.

#### **B. RSA Algorithmic**

RSA includes an open key and a private key. The open key can be known by everyone and is used for scrambling messages. Messages mixed with the open key must be unscrambled in a reasonable proportion of time utilizing the private key. The keys for the RSA computation are made the accompanying way:

1. Pick two unmistakable prime numbers p and q. For security purposes, the whole number's p and q should be picked unpredictably, and should be of near piece length.

2. Figure n = pq. n is used as the modulus for the two individuals when all is said in done and private keys. Its lenth, typically imparted in bits, is the key length.

3. Figure  $\varphi(n) = \varphi(p)\varphi(q) = (p-1)(q-1) = n - (p+q-1)$ , where  $\varphi$  is Euler's totient work.

4. Pick a number e with the ultimate objective that  $1 < e < \varphi(n)$  and  $gcd(e, \varphi(n)) = 1$ ; i.e., e and  $\varphi(n)$  are co prime. e is released as the open key model .e having a short piece length and small Hamming weight achieves continuously powerful encryption – most typically 216 + 1 = 65,537. In any case, much smaller estimations of e, (for instance, 3) have been shown to be less secure in specific settings.

5. Decide d as  $d \equiv e^{-1} \pmod{\phi(n)}$ ; i.e., d is the multiplicative opposite of e (modulo  $\phi(n)$ ). This is even more clearly communicated as: comprehend for d given dxe  $\equiv 1 \pmod{\phi(n)}$ . This is every now and again figured utilizing the comprehensive Euclidean count. Utilizing the pseudocode in the Modular whole numbers section, inputs an and n identify with e and  $\phi(n)$ , independently, d is kept as the private key model.

The open key incorporates the modulus n and general society (or encryption) type e. The private key includes the modulus n and the private (or interpreting) type d, which must be stayed mindful. p, q, and  $\varphi(n)$  should likewise be stayed reasonable considering the way that they can be utilized to figure d.

## **IV. CONCLUSION**

Montgomery Particular multiplier showed to be profitable for the circumstance of locale similarly as timing requirements. Regardless, one more undertaking of increase and measured action must be done. In the equal movement, for every Montgomery particular multiplier there is additional assignment for duplication and measured errand, this will decrease the clock cycle similarly as territory in the chip.

REFERENCE

- 1. J. Ding and S. Li, "A low-latency and low-cost Montgomery modular multiplier based on NLP multiplication," in IEEE Transactions on Circuits and Systems DOI 10.1109/TCSII, 2019.

- 2. A. Parihar and S. Nakhate, "Fast Montgomery modular multiplier for Rivest–Shamir–Adleman cryptosystem," in IET Information Security, vol. 13, no. 3, pp. 231-238, 5 2019.

- 3. J. Li, S. Zhong, Z. Li, S. Cao, J. Zhang and W. Wang, "Speed-Oriented Architecture for Binary Field Point Multiplication on Elliptic Curves," in IEEE Access, vol. 7, pp. 32048-32060, 2019.

- 4. W. Dai, D. Chen, R. C. C. Cheung and Ç. K. Koç, "FFT-Based McLaughlin's Montgomery Exponentiation without Conditional Selections," in IEEE Transactions on Computers, vol. 67, no. 9, pp. 1301-1314, 1 Sept. 2018.

- 5. P. Patronik and S. J. Piestrak, "Hardware/Software Approach to Designing Low-Power RNS-Enhanced Arithmetic Units," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 5, pp. 1031-1039, May 2017.

- 6. S. S. Erdem, T. Yanık and A. Çelebi, "A General Digit-Serial Architecture for Montgomery Modular Multiplication," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 5, pp. 1658-1668, May 2017.

- P. Chen, S. N. Basha, M. Mozaffari-Kermani, R. Azarderakhsh and J. Xie, "FPGA Realization of Low Register Systolic All-One-Polynomial Multipliers Over \$GF(2^{m})\$ and Their Applications in Trinomial Multipliers," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 2, pp. 725-734, Feb. 2017.

- 8. S. NEMA and A. GOUR, "HIGH SPEED AREA EFFICIENT VLSI ARCHITECTURE FOR DCT AND DHT ALGORITHM", IJOSCIENCE, vol. 3, no. 5, May 2017.

- http://ijoscience.com/ojsscience/index.php/ojsscience/article/view/53.

- 9. M. Morales-Sandoval and A. Diaz-Perez, "Scalable GF(p) Montgomery multiplier based on adigit-digitcomputation approach," in IET Computers & Digital Techniques, vol. 10, no. 3, pp. 102-109, 5 2016.

- 10. D. D. Chen, G. X. Yao, R. C. C. Cheung, D. Pao and Ç. K. Koç, "Parameter Space for the Architecture of FFT-Based Montgomery Modular Multiplication," in IEEE Transactions on Computers, vol. 65, no. 1, pp. 147-160, 1 Jan. 2016.

- 11. S. Kuang, K. Wu and R. Lu, "Low-Cost High-Performance VLSI Architecture for Montgomery Modular Multiplication," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 2, pp. 434-443, Feb. 2016.

- Q. Yang, X. Hu and Z. Qin, "Secure Systolic Montgomery Modular Multiplier Over Prime Fields Resilient to Fault-Injection Attacks," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 9, pp. 1889-1902, Sept. 2015.